목차

1. 제목

2. 실험결과

3. 검토 및 평가

본문내용

제목

– 공통 소오스 증폭기

1. 실험 결과

– 회로 사진 및 결과 사진

1.공통 소오스 증폭기 회로

이번 실험에서는 실험과정에서 이상과 현실이 다른 점과 장비의 한계 등을 이유로 책의 실험 절차와 다른 실험 과정으로 진행되었다.

1.R에 걸리는 전압 vO이 5.5V가 되도록 하는 VGG를 찾는다

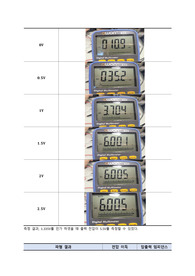

2.VGG가 0~2.5V까지 500mV 씩 증가시키면서 vO를 측정한다.

3.AC전압을 인가하여 VG의 파형과 vO의 파형을 측정하여 전압이득을 계산한다.

4.AC전압을 인가하며 입출력 임피던스를 구한다(입력은 전류가 미세하기에 출력만 구한다.)

측정 결과, 1.335V를 인가 하였을 때 출력 전압이 5.5V를 측정할 수 있었다.

약 10.6배의 전압이득이 발생하였다.

입력의 전류는 아주 미세한 수준에 불과하여 멀티미터 상으로는 측정이 어려워 출력의 전류만 측정하기로 하였다.

하지만 AC전압을 0.02V로 인가하였을 때에는 출력의 전류 측정도 어려워 AC전압의 크기를 1V로 증가시켜서 전류를 측정하였고, 이 때의 전류가 250μA 이다.

출처 : 해피캠퍼스

답글 남기기